P8Z77-M - Motherboard ASUS - Free user manual and instructions

Find the device manual for free P8Z77-M ASUS in PDF.

Questions des utilisateurs sur P8Z77-M ASUS

0 question sur cet appareil. Repondez a celles que vous connaissez ou posez la votre.

Poser une nouvelle question sur cet appareil

Download the instructions for your Motherboard in PDF format for free! Find your manual P8Z77-M - ASUS and take your electronic device back in hand. On this page are published all the documents necessary for the use of your device. P8Z77-M by ASUS.

USER MANUAL P8Z77-M ASUS

Offer to Provide Source Code of Certain Software

This product may contain copyrighted software that is licensed under the General Public License ("GPL") and under the Lesser General Public License Version ("LGPL"). The GPL and LGPL licensed code in this product is distributed without any warranty. Copies of these licenses are included in this product.

You may obtain the complete corresponding source code (as defined in the GPL) for the GPL Software, and/or the complete corresponding source code of the LGPL Software (with the complete machine-readable "work that uses the Library") for a period of three years after our last shipment of the product including the GPL Software and/or LGPL Software, which will be no earlier than December 1, 2011, either

(1) for free by downloading it from http://support.asus.com/download;

or

(2) for the cost of reproduction and shipment, which is dependent on the preferred carrier and the location where you want to have it shipped to, by sending a request to:

ASUSTeK Computer Inc.

Legal Compliance Dept.

15 Li Te Rd.,

Beitou, Taipei 112

Taiwan

In your request please provide the name, model number and version, as stated in the About Box of the product for which you wish to obtain the corresponding source code and your contact details so that we can coordinate the terms and cost of shipment with you.

The source code will be distributed WITHOUT ANY WARRANTY and licensed under the same license as the corresponding binary/object code.

This offer is valid to anyone in receipt of this information.

ASUSTeK is eager to duly provide complete source code as required under various Free Open Source Software licenses. If however you encounter any problems in obtaining the full corresponding source code we would be much obliged if you give us a notification to the email address gpl@asus.com, stating the product and describing the problem (please do NOT send large attachments such as source code archives etc to this email address).

Table des matieres

3.3 Menu Main (Principal) 3-5

Security (Securite) 3-5

3.4 Menu Ai Tweaker 3-7

3.5 Menu Advanced (Avancé) 3-18

3.5.1 CPU Configuration (Configuration du CPU) 3-19

3.5.2 PCH Configuration 3-21

3.5.3 SATA Configuration (Configuration SATA) 3-22

3.5.4 System Agent Configuration (Agent de configuration système) 3-23

3.5.5 USB Configuration (Configuration USB) 3-25

3.5.6 Onboard Devices Configuration (Configuration des périhériques embarqués) 3-26

3.5.7 APM (Gestion d'alimentation avancée) 3-29

3.5.8 Network Stack (Pile réseau) 3-30

3.6 Menu Monitor (Surveillance) 3-31

3.7 Menu Boot (Démarriage) 3-34

3.8 Menu Tools (Outils) 3-35

3.8.1 ASUS EZ Flash 2 Utility 3-35

3.8.2 ASUS O.C. Profile 3-36

3.8.3 ASUS DRAM SPD Information (Informations de SPD). 3-37

3.8.4 ASUS Drive Xpert 3-38

3.9 Menu Exit (Sortie) 3-39

3.10 Mettre a jour le BIOS 3-40

3.10.1 Utilitaire ASUS Update 3-41

3.10.2 Utilitaire ASUS EZ Flash 3-44

3.10.3 Utilitaire ASUS CrashFree BIOS 3. 3-45

3.10.4 Utilitaire ASUS BIOS Updater 3-46

Table des matieres

2.2.3 Central Processing Unit (CPU)

Configurations mémoire

| Code | Description |

| 00 | Not used |

| 01 | Power on. Reset type detection (soft/hard). |

| 02 | AP initialization before microcode loading |

| 03 | System Agent initialization before microcode loading |

| 04 | PCH initialization before microcode loading |

| 06 | Microcode loading |

| 07 | AP initialization after microcode loading |

| 08 | System Agent initialization after microcode loading |

| 09 | PCH initialization after microcode loading |

| 0B | Cache initialization |

| 0C-0D | Reserved for future AMI SEC error codes |

| 0E | Microcode not found |

| 0F | Microcode not loaded |

| 10 | PEI Core is started |

| 11-14 | Pre-memory CPU initialization is started |

| 15-18 | Pre-memory System Agent initialization is started |

| 19-1C | Pre-memory PCH initialization is started |

| 2B-2F | Memory initialization |

| 30 | Reserved for ASL (see ASL Status Codes section below) |

| 31 | Memory Installed |

| 32-36 | CPU post-memory initialization |

| 37-3A | Post-Memory System Agent initialization is started |

| Code | Description |

| 3B - 3E | Post-Memory PCH initialization is started |

| 4F | DXE IPL is started |

| 50 - 53 | Memory initialization error. Invalid memory type or incompatible memory speed |

| 54 | Unspecified memory initialization error |

| 55 | Memory not installed |

| 56 | Invalid CPU type or Speed |

| 57 | CPU mismatch |

| 58 | CPU self test failed or possible CPU cache error |

| 59 | CPU micro-code is not found or micro-code update is failed |

| 5A | Internal CPU error |

| 5B | Reset PPI is not available |

| 5C - 5F | Reserved for future AMI error codes |

| E0 | S3 Resume is stared (S3 Resume PPI is called by the DXE IPL) |

| E1 | S3 Boot Script execution |

| E2 | Video repost |

| E3 | OS S3 wake vector call |

| E4 - E7 | Reserved for future AMI progress codes |

| E8 | S3 Resume Failed |

| E9 | S3 Resume PPI not Found |

| EA | S3 Resume Boot Script Error |

| EB | S3 OS Wake Error |

| EC - EF | Reserved for future AMI error codes |

| F0 | Recovery condition triggered by firmware (Auto recovery) |

| F1 | Recovery condition triggered by user (Forced recovery) |

| F2 | Recovery process started |

| F3 | Recovery firmware image is found |

| F4 | Recovery firmware image is loaded |

| F5 - F7 | Reserved for future AMI progress codes |

| F8 | Recovery PPI is not available |

| F9 | Recovery capsule is not found |

| FA | Invalid recovery capsule |

| FB - FF | Reserved for future AMI error codes |

| 60 | DXE Core is started |

| 61 | NVRAM initialization |

| 62 | Installation of the PCH Runtime Services |

| 63 - 67 | CPU DXE initialization is started |

| 68 | PCI host bridge initialization |

| 69 | System Agent DXE initialization is started |

| 6A | System Agent DXE SMM initialization is started |

| Code | Description |

| 6B - 6F | System Agent DXE initialization (System Agent module specific) |

| 70 | PCH DXE initialization is started |

| 71 | PCH DXE SMM initialization is started |

| 72 | PCH devices initialization |

| 73 - 77 | PCH DXE Initialization (PCH module specific) |

| 78 | ACPI module initialization |

| 79 | CSM initialization |

| 7A - 7F | Reserved for future AMI DXE codes |

| 90 | Boot Device Selection (BDS) phase is started |

| 91 | Driver connecting is started |

| 92 | PCI Bus initialization is started |

| 93 | PCI Bus Hot Plug Controller Initialization |

| 94 | PCI Bus Enumeration |

| 95 | PCI Bus Request Resources |

| 96 | PCI Bus Assign Resources |

| 97 | Console Output devices connect |

| 98 | Console input devices connect |

| 99 | Super IO Initialization |

| 9A | USB initialization is started |

| 9B | USB Reset |

| 9C | USB Detect |

| 9D | USB Enable |

| 9E - 9F | Reserved for future AMI codes |

| A0 | IDE initialization is started |

| A1 | IDE Reset |

| A2 | IDE Detect |

| A3 | IDE Enable |

| A4 | SCSI initialization is started |

| A5 | SCSI Reset |

| A6 | SCSI Detect |

| A7 | SCSI Enable |

| A8 | Setup Verifying Password |

| A9 | Start of Setup |

| AA | Reserved for ASL (see ASL Status Codes section below) |

| AB | Setup Input Wait |

| AC | Reserved for ASL (see ASL Status Codes section below) |

| AD | Ready To Boot event |

| AE | Legacy Boot event |

| AF | Exit Boot Services event |

| B0 | Runtime Set Virtual Address MAP Begin |

| Code | Description |

| B1 | Runtime Set Virtual Address MAP End |

| B2 | Legacy Option ROM Initialization |

| B3 | System Reset |

| B4 | USB hot plug |

| B5 | PCI bus hot plug |

| B6 | Clean-up of NVRAM |

| B7 | Configuration Reset (reset of NVRAM settings) |

| B8-BF | Reserved for future AMI codes |

| D0 | CPU initialization error |

| D1 | System Agent initialization error |

| D2 | PCH initialization error |

| D3 | Some of the Architectural Protocols are not available |

| D4 | PCI resource allocation error. Out of Resources |

| D5 | No Space for Legacy Option ROM |

| D6 | No Console Output Devices are found |

| D7 | No Console Input Devices are found |

| D8 | Invalid password |

| D9 | Error loading Boot Option (LoadImage returned error) |

| DA | Boot Option is failed (StartImage returned error) |

| DB | Flash update is failed |

| DC | Reset protocol is not available |

| Code | Description |

| 0x01 | System is entering S1 sleep state |

| 0x02 | System is entering S2 sleep state |

| 0x03 | System is entering S3 sleep state |

| 0x04 | System is entering S4 sleep state |

| 0x05 | System is entering S5 sleep state |

| 0x10 | System is waking up from the S1 sleep state |

| 0x20 | System is waking up from the S2 sleep state |

| 0x30 | System is waking up from the S3 sleep state |

| 0x40 | System is waking up from the S4 sleep state |

| 0xAAC | System has transitioned into ACPI mode. Interrupt controller is in PIC mode. |

| 0xAA | System has transitioned into ACPI mode. Interrupt controller is in ASIC mode. |

(4-pin CPU_FAN; 4-pin CPU_OPT; 4-pin CHA_FAN1-4)

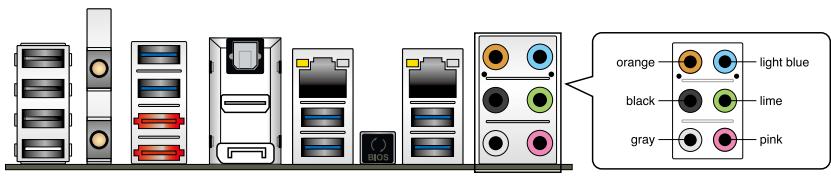

| Port | Casque 2 canaux | 4 canaux | 6 canaux | 8 canaux |

| Bleu clair | Line In | Line In | Line In | Line In |

| Vert | Line Out | Front Speaker Out | Front Speaker Out | Front Speaker Out |

| Rose | Mic In | Mic In | Mic In | Mic In |

| Orange | - | - | Center/Subwoofer | Center/Subwoofer |

| Noir | - | Rear Speaker Out | Rear Speaker Out | Rear Speaker Out |

| Gris | - | - | - | Side Speaker Out |

2.3.13 Connexions audio

Connexions audio

eXtreme Memory Profile [High Performance]

CPU bus speed : DRAM speed ratio mode

DRAM CAS# Latency [Auto]

Configuration options: [Auto] [3 DRAM Clock] - [15 DRAM Clock]

DRAM RAS# to CAS# Delay [Auto]

Configuration options: [Auto] [4 DRAM Clock] - [15 DRAM Clock]

DRAM RAS# PRE Time [Auto]

Configuration options: [Auto] [4 DRAM Clock] - [15 DRAM Clock]

DRAM RAS#ACT Time [Auto]

Configuration options: [Auto] [4 DRAM Clock] - [40 DRAM Clock]

DRAM COMMAND Mode [Auto]

Configuration options: [Auto] [1 DRAM Clock] [2 DRAM Clock] [3 DRAM Clock]

Secondary Timings

DRAM RAS# to RAS# Delay [Auto]

Configuration options: [Auto] [4 DRAM Clock] - [7 DRAM Clock]

DRAM REF Cycle Time [Auto]

Configuration options: [Auto] [48 DRAM Clock] - [511 DRAM Clock]

DRAM Refresh Interval [Auto]

Configuration options: [Auto] [48 DRAM Clock] - [511 DRAM Clock]

DRAM WRITE Recovery Time [Auto]

Configuration options: [Auto] [5 DRAM Clock] - [31 DRAM Clock]

DRAM READ to PRE Time [Auto]

Configuration options: [Auto] [4 DRAM Clock] - [15 DRAM Clock]

DRAM FOUR ACT WIN Time [Auto]

Configuration options: [Auto] [16 DRAM Clock] - [63 DRAM Clock]

DRAM WRITE to READ Delay [Auto]

Configuration options: [Auto] [4 DRAM Clock] - [15 DRAM Clock]

DRAM CKE Minimum pulse width [Auto]

Configuration options: [Auto] [4 DRAM Clock] - [15 DRAM Clock]

DRAM CAS# Write to Latency [Auto]

Configuration options: [Auto] [1 DRAM Clock] - [15 DRAM Clock]

DRAM RTL (CHA) [Auto]

Configuration options: [Auto] [1 DRAM Clock] - [15 DRAM Clock]

DRAM RTL (CHB) [Auto]

Configuration options: [Auto] [1 DRAM Clock] - [15 DRAM Clock]

Third Timings

tWRDR (DD) [Auto]

Configuration options: [Auto] [0 DRAM Clock] - [7 DRAM Clock]

tRWDR (DD) [Auto]

Configuration options: [Auto] [0 DRAM Clock] - [15 DRAM Clock]

tRWSR [Auto]

Configuration options: [Auto] [0 DRAM Clock] - [15 DRAM Clock]

tRR (DD) [Auto]

Configuration options: [Auto] [0 DRAM Clock] - [7 DRAM Clock]

tRR (DR) [Auto]

Configuration options: [Auto] [0 DRAM Clock] - [7 DRAM Clock]

tRRSR [Auto]

Configuration options: [Auto] [0 DRAM Clock] - [15 DRAM Clock]

tWW (DD) [Auto]

Configuration options: [Auto] [0 DRAM Clock] - [7 DRAM Clock]

tWW (DR) [Auto]

Configuration options: [Auto] [0 DRAM Clock] - [7 DRAM Clock]

tWWSR [Auto]

Configuration options: [Auto] [0 DRAM Clock] - [15 DRAM Clock]

MRC Fast Boot

Long Duration Maintained [Auto]

Short Duration Power Limit [Auto]

Additional Turbo Voltage [Auto]

Primary Plane Current Limit [Auto]

CPU Power Duty Control [T.Probe]

VCCSA Voltage (Voltage VCCSA) [Auto]

Intel Adaptive Thermal Monitor

Adjacent Cache Line Prefetcher [Enabled]

[Enabled] Active la fonction Adjacent Cache Line Prefetcher.

[Disabled] Désactive cette option.

Enhanced Intel SpeedStep Technology (Technologie EIST) [Enabled]

Permet d'activer ou désactiver la technologie EIST (Enhanced Intel® SpeedStep Technology).

[Enabled] Enables the C1E support function. This item should be enabled in order to enable the Enhanced Halt State.

[Disabled] Disables this function.

CPU C3 Report [Auto]

SATA Mode Selection (Selection de mode SATA) [AHCI Mode]

Allows you to enable remapping the memory above 4GB.

Legacy USB Support (Support USB hérié) [Enabled]

Marvell Storage Firmware Check and Update

Anti Surge Support (Support Anti Surge) [Enabled]

[Enable both UEFI and Legacy]

[DisableUEFI]

Discard Changes & Exit

Launch EFI Shell from filesystem device (Lancer l'application EFI Shell)

Lancer USB 3.0 Boost

4.3.6 Assistant USB BIOS Flashback

Lancer Sensor Recorder

WARNING ALL DATA ON SELECTED SYSTEM WILL BE LAST. Are you sure you want to create this volume? (Y/N):

Demarrer AMD Catalyst Control Center

Pour démarrer AMD Catalyst Control Center

DECLARATION OF CONFORMITY

Per FCC Part 2 Section 2.1077(a)

Responsible Party Name: Asus Computer International

Address: 800 Corporate Way, Fremont, CA 94539.

Phone/Fax No: (510)739-3777/(510)608-4555

Product Name : Motherboard

Model Number : P8Z77-V Delu

Conforms to the following specifications:

FCC Part 15, Subpart B, Unintentional Radiators

FCC Part 15, Subpart C, Intentional Radiators

FCC Part 15, Subpart E, Intentional Radiators

Supplementary Information:

This device complies with part 15 of the FCC Rules. Operation is subject to the following two conditions: (1) This device may not cause harmful interference, and (2) this device must accept any interference received, including interference that may cause undesired operation.

Representative Person's Name: Steve Chang / President

Date: Jan.06,2012

Signature

Year to begin affixing CE marking:2012

(EC conformity marking)

Position:CEO

Name: -Jerry

12x - 1 > 0

EasyManual

EasyManual